# Experiment 8 Transistor Characteristics

### 1 Motivation

Like diodes, transistors are a fundamental element of modern electronics. They are used as amplifiers in signal processing and as voltage-controlled switches. They are the building block for operational amplifier integrated circuits used in a wide array of linear and nonlinear circuit applications. As switches, they are used to construct gates in digital logic circuitry.

## 2 Background

A transistor is a 3-terminal "active" electronic component, meaning one that behaves as if it has an internal source (current or voltage). There are two main categories of transistors, bipolar-junction (BJT) and field-effect (FET). Each is based on P-N semiconductor junctions. The BJT behaves as a current-controlled current source, and the FET behaves as a voltage-controlled current source. This makes them useful as voltage and current amplifiers. Both can be used as switches. The MOSFET version of the FET has enormous input resistance and is preferred for constructing logic gates.

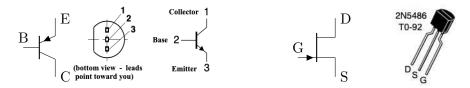

In this experiment you will investigate the basic properties of the PNP version of the BJT and the N-channel version of the junction field-effect transistor (JFET). The part schematics and package illustrations for these are shown in Fig. 1.

**CAUTION!** It is easy to get confused when you turn the transistors over to install them in the socket on the circuit board. You are now looking at the top.

Figure 1: Circuit schematics and lead diagrams for bipolar-junction PNP (2N3906) and N-Channel JFET (2N5486). It is standard to show as bottom view of the leads for transistors (and vacuum tubes). Perversely, integrated circuits are always shown from the top.

### 3 Equipment

For this experiment, you will use:

- One Topward dual DC power supply, set for independent supplies (slide switches)

- Two DMM4020 digital multimeters

- Two Keithley digital multimeters

- One circuit board for testing transistors

- One ELC variable resistance box

- One 2N3906 PNP BJT transistor (parts cabinet)

- One 2N5486 N-CHAN JFET transistor (parts cabinet)

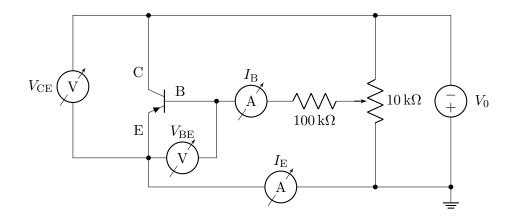

Figure 2: Circuit for characterizing a bipolar junction transistor. Note the polarity of the DC voltage source, which is shown appropriate for a PNP transistor. The polarity would be opposite when working with an NPN transistor.

### 4 Procedure

- 1. The Bipolar Junction Transistor (2N3906): The schematic for the circuit board for testing transistors is shown in Fig. 2. To complete the circuit, you will first add the four meters shown in the schematic before adding the DC voltage supply. Use a Keithley DMM on the 200 µA scale to measure  $I_{\rm B}$ . Use the other Keithley DMM to measure  $I_{\rm E}$ . Use the two Tektronix DMM's to measure  $V_{\rm CE}$  and  $V_{\rm BE}$  (via the V $\Omega$  HI-LO inputs on the left). Please be careful setting up the meters! A current meter has very low (ideally zero) resistance and must be connected in series within a branch of a circuit. If you accidentally place an ammeter across two points in a circuit, the short circut can cause large current to flow that damages components.

- (a) Begin by measuring  $I_{\rm E}$  and  $V_{\rm BE}$  as a function of the base current,  $I_{\rm B}$ , for a fixed value of  $V_{\rm CE}$ . To do this, complete the circuit as follows: (1) turn the 10 k $\Omega$  potentiometer all the way counter-clockwise until the knob stops, which moves the wiper to ground. (2) Connect the ammeters noting their polarity for direction of the current. (3) Connect the voltmeters and the DC voltage supply, being careful to observe polarities. (4) The circuit is mostly prewired (look at the underside of the board), but you need to add one banana patch cable between the terminals for  $V_0$  and the transistor's collector. After double checking your connections, (5) insert the transistor into the socket on the circuit board and then turn on the source and adjust  $V_0$  until  $V_{\rm CE} = -12$  V.

- (b) Turning the potentiometer will change the base-to-emitter voltage,  $V_{\rm BE}$ , and therefore the base current  $I_{\rm B}$ . Measure and tabulate  $I_{\rm E}$  and  $V_{\rm BE}$  as a function of  $I_{\rm B}$ . Increase  $I_{\rm B}$ in 2µA steps from  $0 < I_{\rm B} < 10$ µA and then 10µA steps from  $10 < I_{\rm B} < 50$ µA. You will notice that  $V_{\rm BE}$  drifts slowly when  $I_{\rm B}$  is increased or decreased. This drift is caused by heating of the transistor's P-N junctions, which are sensitive to temperature. Pause briefly after each change in  $I_{\rm B}$  to allow the temperature to stabilize before taking your readings. Calculate  $\beta$  (aka  $h_{fe}$ ) for your data using  $\beta = I_{\rm C}/I_{\rm B}$  and make a graph of  $\beta$ versus  $I_{\rm E}$ .

- (c) Measure the input resistance,  $r_{\rm in}$  ( $h_{ie}$ ), as follows: keeping  $V_{\rm CE}$  constant (e.g,  $V_{\rm CE} = -8 \,\mathrm{V}$ ), set  $I_{\rm B} = 6 \,\mu\mathrm{A}$  and measure  $I_{\rm E}$  and  $V_{\rm BE}$  then repeat for  $I_{\rm B} = 10 \,\mu\mathrm{A}$ . Calculate

the input resistance using Eq. 1. (A typical value is  $h_{ie} = 3.5 \,\mathrm{k\Omega}$ .)

$$h_{ie} = \left(\frac{\delta V_{\rm BE}}{\delta I_{\rm B}}\right)_{V_{\rm CE}=constant} \tag{1}$$

- (d) Table 8.1 in Sprott summarizes a comparison of the models for the "ideal" and "real" transistor with the more complete *T*-network shown in Fig. 8.5(a). For the "real" transistor, the input resistance,  $r_{\rm in}$ , is related to the "transresistance" by  $r_{\rm in} = (\beta+1)r_{tr} \approx \beta r_{tr}$ , where  $\beta = h_{fe}$  is the current gain. The first row in Table 8.1 gives the equivalents for  $h_{ie}$  (the input resistance you found above). In the entry under "*T*-network", the base resistance,  $r_{\rm B}$ , is typically small and can be ignored. Also, since  $r_{\rm C} \gg r_{\rm E}$ , the parallel combination  $r_{\rm C}||r_{\rm E} \approx r_{\rm E}$ , so  $h_{ie} \approx \beta r_{\rm E}$ . In this approximation, the transresistance,  $r_{tr}$ , is the same as  $r_{\rm E}$ . These are used interchangeably in Sprott's text. Calculate  $\beta = h_{fe} = \delta I_{\rm E}/\delta I_{\rm B}$  for your measurements in step (c) and then determine  $r_{tr}$ . Compare your result with the expected value,  $r_{tr} \approx r_d \approx 26 \,\mathrm{mV}/\langle I_{\rm E}\rangle$ , where  $\langle I_{\rm E}\rangle$  is the average of the two values from step (c), and  $r_d$  is the "dynamic resistance" (Sprott Eq. 8.3).

- (e) (*Optional, come back if time remains*) For signal transistors like the 2N3906, the relationship between  $V_{\rm BE}$  and  $I_{\rm E}$  is given approximately by

$$I_{\rm E} = I_0 \left( e^{eV_{\rm BE}/kT} - 1 \right).$$

(2)

The *I-V* characteristic depends on (absolute) temperature, *T*, because the electron thermal velocity affects diffusion across the P-N junction. Technically, parameter  $I_0$  also depends on *T*, but Eq. 2 is a good approximation for fixed *T*. Make a semi-log plot of  $I_E$ vs  $V_{BE}$  and verify that the low-current region is linear (in semi-log). You can determine  $eV_{BE}/kT$  from the slope of a linear fit to your data, assuming that  $eV_{BE}/kT \gg 1$ . How does your result compare with the expected value,  $e/kT \approx 26 \text{ mV}$  for room temperature? This temperature dependence is interesting physics, but it is rarely important in transistor applications.

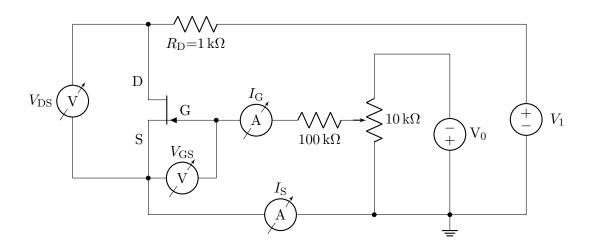

Figure 3: Circuit for characterizing a field-effect transistor. Note the polarity of the DC voltage sources, which are shown appropriate for an N-Channel FET. The polarities would be opposite when testing a P-Channel FET.

- 2. The Field-Effect Transistor (2N5486): You will now measure the properties of an Nchannel junction field-effect transistor (JFET). The setup is shown in Fig. 3, which is almost the same as before but with two additions. For a JFET, the potentials between the gate and drain relative to the source have opposite signs, so you need to add a second DC supply,  $V_1$ , to provide (positive) voltage at the drain. You also need to add resistor  $R_D$ . Note that the lead order of the 2N5486 package is different than the 2N3906 package. (In actual applications, the DC operating point can be established using one DC voltage supply and additional resistors.)

- (a) Make sure you ground the negative terminal of the  $V_1$  supply and the positive terminal of the  $V_0$  supply. The DMMs measure the source current,  $I_S$ , the gate current,  $I_G$ , and the voltages,  $V_{DS}$  and  $V_{GS}$ . From Kirchhoff's current rule, the drain current  $I_D = I_S I_G$ . After double checking the connections and polarities, turn on the power supplies and set  $V_0 = -5$  V and  $V_1 = 0$  V.

- (b) An FET can be used as a voltage-controlled variable resistor. The resistance of the drainsource channel is adjusted by varying the gate voltage,  $V_{\rm GS}$ . (Internally this changes the width of the depletion region.) Turn the potentiometer fully CCW so that  $V_{\rm GS} = 0$ . Now vary  $V_{\rm DS}$  (by adjusting  $V_1$ ) from 0 V to +2.0 V in 0.2 V steps and from +2.0 V to +10.0 V in 2.0 V steps. You should see that  $I_{\rm G}$  is always very small, hence  $I_{\rm D} = I_{\rm S}$ . Why is  $I_{\rm G}$  small? Tabulate your data and make a plot of  $I_{\rm D}$  versus  $V_{\rm DS}$ . Determine the resistance of the drain-source channel,  $R_{\rm DS}$ , from the ohmic (linear) region of the plot.

- (c) Now measure the characteristics of the JFET in the "pinch-off" region where  $I_{\rm D}$  is nearly independent of  $V_{\rm DS}$ , i.e., the transistor acts like a current source. This is the region where a JFET is used as an amplifier. Set  $V_{\rm GS} = -1.5$  V by adjusting the potentiometer, and then vary  $V_{\rm DS}$  from +2.0 V to +20 V in 2.0 V steps. Tabulate your data and make a plot of  $I_{\rm D}$  versus  $V_{\rm DS}$ .

- (d) In the "pinch-off" region, the JFET behaves like a voltage-controlled current source. Use your data from steps (b) and (c) for  $V_{\rm DS} = +10\,{\rm V}$  to determine the "forward transconductance". (A typical value is  $g_{fs} = 5\,{\rm m}\mathcal{O}$ .)

$$g_{fs} = \left(\frac{\delta I_{\rm D}}{\delta V_{\rm GS}}\right)_{V_{\rm DS}=constant} \tag{3}$$

- (e) As a nearly ideal current source, a JFET has a large but finite output resistance,  $r_{\rm os}$  (see the equivalent circuit in Sprott Fig. 7.16). Evalutate the output resistance in the pinch-off region,  $r_{\rm os} = \delta V_{\rm DS} / \delta I_{\rm D}$ , using your measurements from step (c) with  $V_{\rm DS} = +10$  V and +20 V.

- (f) FET's (usually MOSFETs) are very useful as switches and gates. The "switch" is closed when  $V_{\rm GS} = 0$  and open when  $|V_{\rm GS}| > |V_{\rm P}|$ , the critical pinch-off voltage (also called  $V_{\rm GS(off)}$ ). With  $V_{\rm DS} = +12$  V, vary the potentiometer to change the gate-source voltage,  $V_{\rm GS}$ . Measure and tabulate  $I_{\rm D}$  as a function of  $V_{\rm DS}$  by varying  $V_{\rm GS} = 0$  V in -0.5 V steps up to the critical pinch-off voltage. (You can adjust  $V_1$  to maintain  $V_{\rm DS} = +12$  V.) Plot  $I_{\rm D}$  versus  $V_{\rm GS}$  and determine the "off" voltage for the JFET. The plot should look roughly parabolic as  $V_{\rm GS}$  approaches  $V_{\rm P}$ .

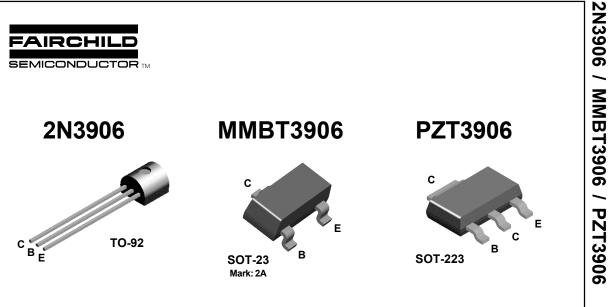

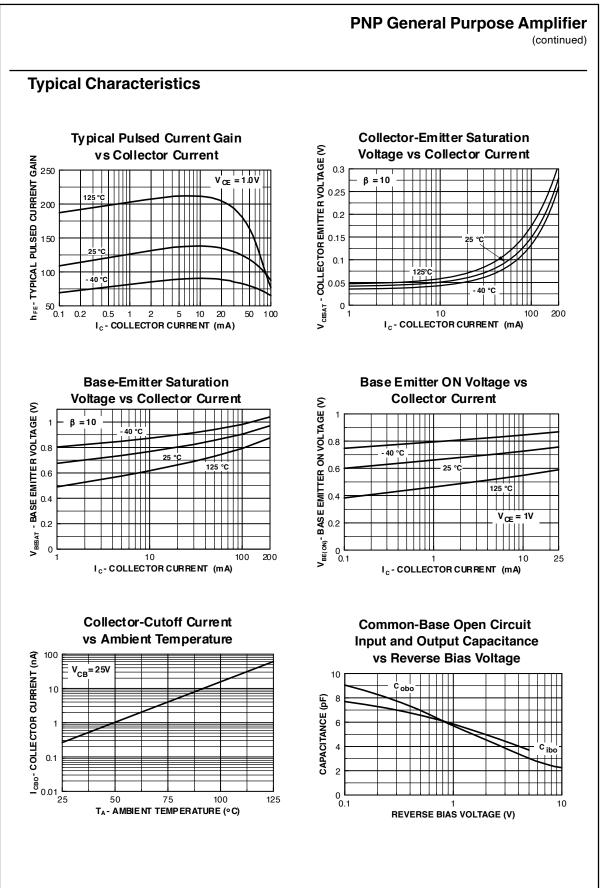

# **PNP General Purpose Amplifier**

This device is designed for general purpose amplifier and switching applications at collector currents of 10  $\mu\text{A}$  to 100 mA.

### Absolute Maximum Ratings\* $T_A = 25^{\circ}C$ unless otherwise noted

| Symbol                            | Parameter                                        | Value       | Units |

|-----------------------------------|--------------------------------------------------|-------------|-------|

| V <sub>CEO</sub>                  | Collector-Emitter Voltage                        | -40         | V     |

| V <sub>CBO</sub>                  | Collector-Base Voltage                           | -40         | V     |

| V <sub>EBO</sub>                  | Emitter-Base Voltage                             | -5.0        | V     |

| I <sub>C</sub>                    | Collector Current - Continuous                   | -200        | mA    |

| T <sub>J</sub> , T <sub>stg</sub> | Operating and Storage Junction Temperature Range | -55 to +150 | °C    |

\*These ratings are limiting values above which the serviceability of any semiconductor device may be impaired.

### NOTES:

1) These ratings are based on a maximum junction temperature of 150 degrees C.

2) These are steady state limits. The factory should be consulted on applications involving pulsed or low duty cycle operations.

### Thermal Characteristics T<sub>A</sub> = 25°C unless otherwise noted

| Symbol          | Characteristic                                | Мах        |            |              | Units       |

|-----------------|-----------------------------------------------|------------|------------|--------------|-------------|

|                 |                                               | 2N3906     | *MMBT3906  | **PZT3906    |             |

| P <sub>D</sub>  | Total Device Dissipation<br>Derate above 25°C | 625<br>5.0 | 350<br>2.8 | 1,000<br>8.0 | mW<br>mW/°C |

| $R_{\theta JC}$ | Thermal Resistance, Junction to Case          | 83.3       |            |              | °C/W        |

| $R_{\theta JA}$ | Thermal Resistance, Junction to Ambient       | 200        | 357        | 125          | °C/W        |

\*Device mounted on FR-4 PCB 1.6" X 1.6" X 0.06."

\*\* Device mounted on FR-4 PCB 36 mm X 18 mm X 1.5 mm; mounting pad for the collector lead min. 6 cm<sup>2</sup>.

### **PNP General Purpose Amplifier** (cc

-0.95

٧

| С | nti | nu | ed) |

|---|-----|----|-----|

| Electrical Characteristics T <sub>A</sub> = 25°C unless otherwise noted |                                      |                                                                                                         |           |       |       |  |

|-------------------------------------------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------|-----------|-------|-------|--|

| Symbol                                                                  | Parameter                            | Test Conditions                                                                                         | Min       | Max   | Units |  |

| OFF CHAF                                                                | RACTERISTICS                         |                                                                                                         |           |       |       |  |

| V <sub>(BR)CEO</sub>                                                    | Collector-Emitter Breakdown Voltage* | I <sub>C</sub> = -1.0 mA, I <sub>B</sub> = 0                                                            | -40       |       | V     |  |

| V <sub>(BR)CBO</sub>                                                    | Collector-Base Breakdown Voltage     | $I_{\rm C} = -10 \mu {\rm A},  I_{\rm E} = 0$                                                           | -40       |       | V     |  |

| V <sub>(BR)EBO</sub>                                                    | Emitter-Base Breakdown Voltage       | $I_{\rm E} = -10 \mu {\rm A},  I_{\rm C} = 0$                                                           | -5.0      |       | V     |  |

| BL                                                                      | Base Cutoff Current                  | V <sub>CE</sub> = -30 V, V <sub>BE</sub> = -3.0 V                                                       |           | -50   | nA    |  |

| ICEX                                                                    | Collector Cutoff Current             | $V_{CE} = -30 \text{ V}, \text{ V}_{BE} = -3.0 \text{ V}$                                               |           | -50   | nA    |  |

|                                                                         | ACTERISTICS                          |                                                                                                         |           | T     |       |  |

| h <sub>FE</sub>                                                         | DC Current Gain *                    | $I_{c} = -0.1 \text{ mA}, V_{CE} = -1.0 \text{ V}$                                                      | 60        |       |       |  |

|                                                                         |                                      | $I_{C} = -1.0 \text{ mA}, V_{CE} = -1.0 \text{ V}$<br>$I_{C} = -10 \text{ mA}, V_{CE} = -1.0 \text{ V}$ | 80<br>100 | 300   |       |  |

|                                                                         |                                      | $I_{\rm C} = -50 \text{ mA}, V_{\rm CE} = -1.0 \text{ V}$                                               | 60        | 000   |       |  |

|                                                                         |                                      | $V_{C} = -100 \text{ mA}, V_{CE} = -1.0 \text{ V}$                                                      | 30        |       |       |  |

| V <sub>CE(sat)</sub>                                                    | Collector-Emitter Saturation Voltage | $I_{\rm C} = -10$ mA, $I_{\rm B} = -1.0$ mA                                                             |           | -0.25 | V     |  |

|                                                                         |                                      | $I_{\rm C} = -50 \text{ mA}, I_{\rm B} = -5.0 \text{ mA}$                                               |           | -0.4  | V     |  |

| V <sub>BE(sat)</sub>                                                    | Base-Emitter Saturation Voltage      | $I_{\rm C}$ = -10 mA, $I_{\rm B}$ = -1.0 mA                                                             | -0.65     | -0.85 | V     |  |

### SMALL SIGNAL CHARACTERISTICS

| f <sub>T</sub>   | Current Gain - Bandwidth Product | $I_{C}$ = -10 mA, $V_{CE}$ = -20 V,<br>f = 100 MHz                                  | 250 |      | MHz |

|------------------|----------------------------------|-------------------------------------------------------------------------------------|-----|------|-----|

| C <sub>obo</sub> | Output Capacitance               | $V_{CB} = -5.0 \text{ V}, I_E = 0,$<br>f = 100 kHz                                  |     | 4.5  | pF  |

| Cibo             | Input Capacitance                | $V_{EB}$ = -0.5 V, I <sub>C</sub> = 0,<br>f = 100 kHz                               |     | 10.0 | pF  |

| NF               | Noise Figure                     | $I_{C}$ = -100 μA, $V_{CE}$ = -5.0 V,<br>R <sub>S</sub> =1.0 kΩ f=10 Hz to 15.7 kHz |     | 4.0  | dB  |

$I_{\rm C} = -50 \text{ mA}, I_{\rm B} = -5.0 \text{ mA}$

### SWITCHING CHARACTERISTICS

| t <sub>d</sub> | Delay Time   | $V_{CC}$ = -3.0 V, $V_{BE}$ = -0.5 V,              | 35  | ns |

|----------------|--------------|----------------------------------------------------|-----|----|

| t <sub>r</sub> | Rise Time    | I <sub>C</sub> = -10 mA, I <sub>B1</sub> = -1.0 mA | 35  | ns |

| ts             | Storage Time | $V_{\rm CC}$ = -3.0 V, I <sub>C</sub> = -10 mA     | 225 | ns |

| t <sub>f</sub> | Fall Time    | $I_{B1} = I_{B2} = -1.0 \text{ mA}$                | 75  | ns |

\*Pulse Test: Pulse Width  $\leq$  300  $\mu$ s, Duty Cycle  $\leq$  2.0%

### **Spice Model**

PNP (Is=1.41f Xti=3 Eg=1.11 Vaf=18.7 Bf=180.7 Ne=1.5 Ise=0 Ikf=80m Xtb=1.5 Br=4.977 Nc=2 Isc=0 Ikr=0 Rc=2.5 Cjc=9.728p Mjc=.5776 Vjc=.75 Fc=.5 Cje=8.063p Mje=.3677 Vje=.75 Tr=33.42n Tf=179.3p Itf=.4 Vtf=4 Xtf=6 Rb=10)

2N3906 / MMBT3906 / PZT3906

This device is designed primarily for electronic switching applications such as low On Resistance analog switching. Sourced from Process 50.

### Absolute Maximum Ratings\* TA = 25°C unless otherwise noted

| Symbol                           | Parameter                                        | Value       | Units |

|----------------------------------|--------------------------------------------------|-------------|-------|

| V <sub>DG</sub>                  | Drain-Gate Voltage                               | 25          | V     |

| $V_{GS}$                         | Gate-Source Voltage                              | - 25        | V     |

| $I_{GF}$                         | Forward Gate Current                             | 10          | mA    |

| T <sub>J</sub> ,T <sub>stg</sub> | Operating and Storage Junction Temperature Range | -55 to +150 | °C    |

\*These ratings are limiting values above which the serviceability of any semiconductor device may be impaired.

NOTES:

1) These ratings are based on a maximum junction temperature of 150 degrees C.

2) These are steady state limits. The factory should be consulted on applications involving pulsed or low duty cycle operations.

### Thermal Characteristics TA = 25°C unless otherwise noted

| Symbol          | Characteristic                          | Мах    |           | Units |

|-----------------|-----------------------------------------|--------|-----------|-------|

|                 |                                         | 2N5484 | *MMBF5484 |       |

| P <sub>D</sub>  | Total Device Dissipation                | 350    | 225       | mW    |

|                 | Derate above 25°C                       | 2.8    | 1.8       | mW/°C |

| $R_{\theta JC}$ | Thermal Resistance, Junction to Case    | 125    |           | °C/W  |

| $R_{	heta JA}$  | Thermal Resistance, Junction to Ambient | 357    | 556       | °C/W  |

\*Device mounted on FR-4 PCB 1.6" X 1.6" X 0.06."

ã 1997 Fairchild Semiconductor Corporation

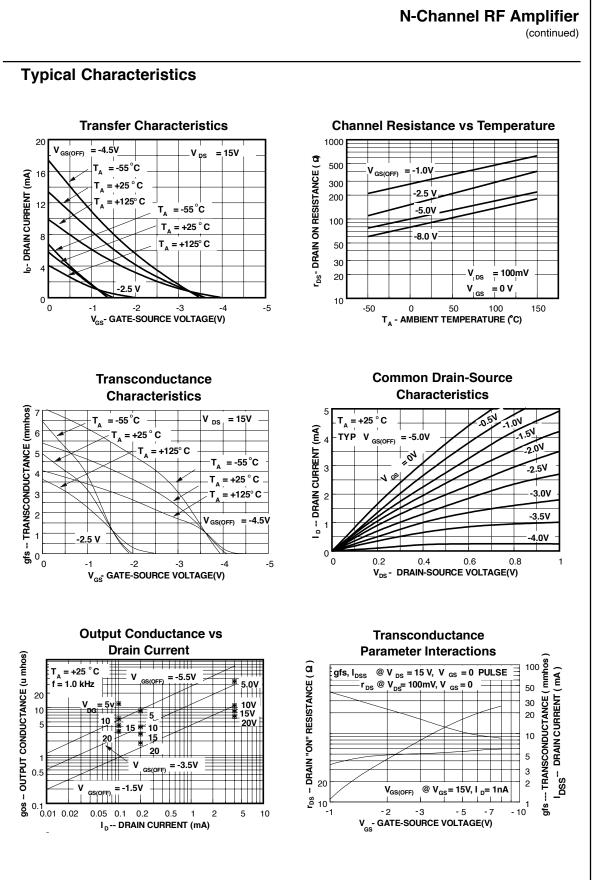

# N-Channel RF Amplifier (continued)

| Electr               | ical Characteristics             | TA = 25°C unless otherwise noted                                                                                                                                                                        |                         |     |                         |                         |

|----------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----|-------------------------|-------------------------|

| Symbol               | Parameter                        | Test Conditions                                                                                                                                                                                         | Min                     | Тур | Max                     | Units                   |

| OFF CHA              | RACTERISTICS                     |                                                                                                                                                                                                         |                         |     |                         |                         |

| V <sub>(BR)GSS</sub> | Gate-Source Breakdown Voltage    | $I_{G} = -1.0 \ \mu A, \ V_{DS} = 0$                                                                                                                                                                    | - 25                    |     |                         | V                       |

| I <sub>GSS</sub>     | Gate Reverse Current             | $V_{GS} = -20 V, V_{DS} = 0$                                                                                                                                                                            |                         |     | - 1.0<br>- 0.2          | nA<br>μA                |

| V <sub>GS(off)</sub> | Gate-Source Cutoff Voltage       | $\label{eq:V_GS} \begin{array}{c} V_{GS} = -\ 20\ V, \ V_{DS} = 0, \ T_A = 100^\circ C \\ V_{DS} = 15\ V, \ I_D = 10\ nA \\ 2N5484 \\ 2N5485 \\ 2N5486 \end{array}$                                     | - 0.3<br>- 0.5<br>- 2.0 |     | - 3.0<br>- 4.0<br>- 6.0 | V<br>V<br>V             |

| ON CHAF              | ACTERISTICS                      |                                                                                                                                                                                                         |                         |     |                         |                         |

| I <sub>DSS</sub>     | Zero-Gate Voltage Drain Current* | $V_{DS} = 15 V, V_{GS} = 0$ 2N5484 2N5485 2N5486                                                                                                                                                        | 1.0<br>4.0<br>8.0       |     | 5.0<br>10<br>20         | mA<br>mA<br>mA          |

| SMALL S              | IGNAL CHARACTERISTICS            |                                                                                                                                                                                                         |                         |     |                         |                         |

| 9fs                  | Forward Transfer Conductance     | $V_{DS} = 15, V_{GS} = 0, f = 1.0 \text{ kHz}$<br>2N5484<br>2N5485<br>2N5485                                                                                                                            | 3000<br>3500<br>4000    |     | 6000<br>7000<br>8000    | μmhos<br>μmhos          |

| Re <sub>(yis)</sub>  | Input Conductance                | $\begin{tabular}{ c c c c c } \hline $2$N5486 \\ \hline $V_{DS}$ = 15, $V_{GS}$ = 0, $f$ = 100 $MHz$ \\ \hline $2$N5484 \\ \hline $V_{DS}$ = 15, $V_{GS}$ = 0, $f$ = 400 $MHz$ \\ \hline \end{tabular}$ | 4000                    |     | 100                     | μmhos<br>μmhos          |

|                      |                                  | 2N5485 / 2N5486                                                                                                                                                                                         |                         |     | 1000                    | μmhos                   |

| g <sub>os</sub>      | Output Conductance               | $V_{DS} = 15, V_{GS} = 0, f = 1.0 \text{ kHz}$<br>2N5484<br>2N5485<br>2N5486                                                                                                                            |                         |     | 50<br>60<br>75          | μmhos<br>μmhos<br>μmhos |

| Re <sub>(yos)</sub>  | Output Conductance               | $V_{DS} = 15, V_{GS} = 0, f = 100 \text{ MHz}$ $2N5484$ $V_{DS} = 15, V_{GS} = 0, f = 400 \text{ MHz}$                                                                                                  |                         |     | 75                      | μmhos                   |

|                      |                                  | 2N5485 / 2N5486                                                                                                                                                                                         |                         |     | 100                     | μmhos                   |

| Re <sub>(yfs)</sub>  | Forward Transconductance         | $V_{DS} = 15, V_{GS} = 0, f = 100 \text{ MHz}$<br><b>2N5484</b><br>$V_{DS} = 15, V_{GS} = 0, f = 400 \text{ MHz}$                                                                                       | 2500                    |     |                         | μmhos                   |

|                      |                                  | 2N5485<br>2N5486                                                                                                                                                                                        | 3000<br>3500            |     |                         | μmhos<br>μmhos          |

| Ciss                 | Input Capacitance                | $V_{DS} = 15, V_{GS} = 0, f = 1.0 \text{ MHz}$                                                                                                                                                          |                         |     | 5.0                     | pF                      |

| C <sub>rss</sub>     | Reverse Transfer Capacitance     | $V_{DS} = 15, V_{GS} = 0, f = 1.0 \text{ MHz}$                                                                                                                                                          |                         |     | 1.0                     | pF                      |

| C <sub>oss</sub>     | Output Capacitance               | $V_{DS} = 15, V_{GS} = 0, f = 1.0 \text{ MHz}$                                                                                                                                                          |                         |     | 2.0                     | pF                      |

| NF                   | Noise Figure                     | $V_{DS}$ = 15 V, $R_G$ = 1.0 k $\Omega$ ,<br>f = 100 MHz 2N5484                                                                                                                                         |                         |     | 3.0                     | dB                      |

|                      |                                  |                                                                                                                                                                                                         |                         | 4.0 |                         | dB                      |

|                      |                                  | f = 100 MHz 2N5485 / 2N5486 $V_{DS}$ = 15 V, R <sub>G</sub> = 1.0 kΩ,                                                                                                                                   |                         |     | 2.0                     | dB                      |

|                      |                                  | f = 400 MHz 2N5485 / 2N5486                                                                                                                                                                             |                         |     | 4.0                     | dB                      |

\*Pulse Test: Pulse Width £ 300 ms, Duty Cycle £ 2%

# 2N5484 / 2N5485 / 2N5486 / MMBF5484 / MMBF5485 / MMBF5486

2N5484 / 2N5485 / 2N5486 / MMBF5484 / MMBF5485 / MMBF5486