# Ph 623 Tre Mar 24

- HW 7 due (email to Joelle

- Oscillator prelab due tomorrow. Lab is due the following Wed.

- Midterm II a week from Thursday

Today:

(i) A Few more number systems

(2) Parakel Logic (Everythin, That can be described by a truth table)

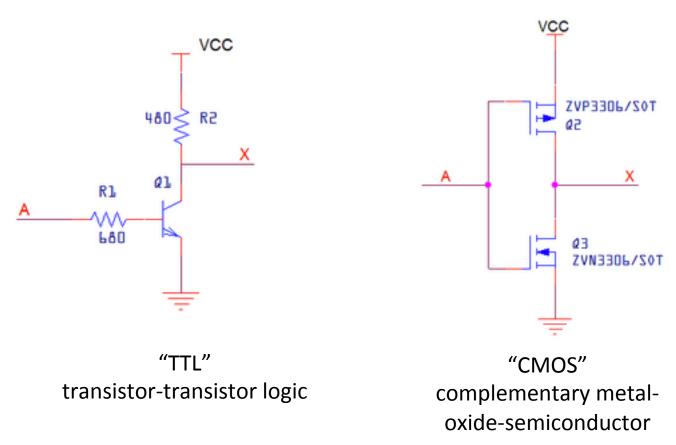

## Logic "Families"

nomenclature: 74LS157

NAND

$$X = \overline{A \cdot B}$$

$A = A$

NOR

$$X = \overline{A + B}$$

$A = A$

XNOR

$$X = \overline{A \oplus B}$$

$\xrightarrow{A}$   $\xrightarrow{B}$

| 1  | 7401 Quad 2-input, open collector output |

|----|------------------------------------------|

| 1. |                                          |

| 1  | 7410 Triple 3-input                      |

| 1  | 7420 Dual 4-input                        |

| 0  | 7430 Single 8-input                      |

|    | 0                                        |

| Α | В           | X |                     |

|---|-------------|---|---------------------|

| 0 | 0           | 1 | 7402 Quad 2-input   |

| 0 | 0<br>1<br>0 | 0 | 7427 Triple 3-input |

| 1 | 0           | 0 | 7425 Dual 4-input   |

| 1 | 1           | 0 |                     |

| Α | В                | X |                    |

|---|------------------|---|--------------------|

| 0 | 0<br>1<br>0<br>1 | 1 |                    |

| 0 | 1                | 0 | 74266 Quad 2-input |

| 1 | 0                | 0 |                    |

| 1 | 1                | 1 |                    |

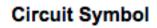

#### **Truth Table**

### Description

| A | В | s | X |

|---|---|---|---|

| 0 | Х | 0 | 0 |

| 1 | X | 0 | 1 |

| X | 0 | 1 | 0 |

| X | 1 | 1 | 1 |

2-input multiplexer

"Data Selector"

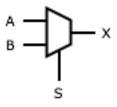

| A | В | С | D | S <sub>1</sub> | $\mathbf{S}_{0}$                | X |

|---|---|---|---|----------------|---------------------------------|---|

| 0 | Х | Х | Х | 0              | 0                               | 0 |

| 1 | Х | X | Х | 0              | 0                               | 1 |

| Х | 0 | Х | X | 0              | 1                               | 0 |

| Х | 1 | X | Х | 0              | 1                               | 1 |

| Х | X | 0 | X | 1              | 0                               | 0 |

| Х | Х | 1 | X | 1              | 0                               | 1 |

| Х | Х | Х | 1 | 1              | 1                               | 0 |

| X | X | X | 1 | 1              | 0<br>0<br>1<br>1<br>0<br>0<br>1 | 1 |

4-input multiplexer

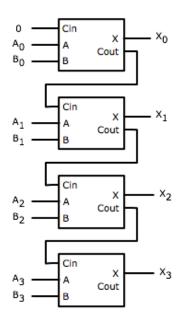

| 1 | 1 | 1 | 1 |   | Су |

|---|---|---|---|---|----|

|   | 1 | 0 | 1 | 1 | A  |

| + | 0 | 1 | 1 | 1 | В  |

| 1 | 0 | 0 | 1 | 0 | '  |

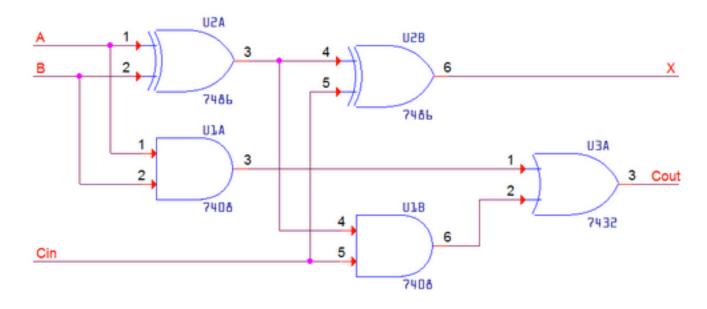

| Cin | A | В | X | Cout |

|-----|---|---|---|------|

| 0   | 0 | 0 | 0 | 0    |

| 0   | 0 | 1 | 1 | 0    |

| 0   | 1 | 0 | 1 | 0    |

| 0   | 1 | 1 | 0 | 1    |

| 1   | 0 | 0 | 1 | 0    |

| 1   | 0 | 1 | 0 | 1    |

| 1   | 1 | 0 | 0 | 1    |

| 1   | 1 | 1 | 1 | 1    |

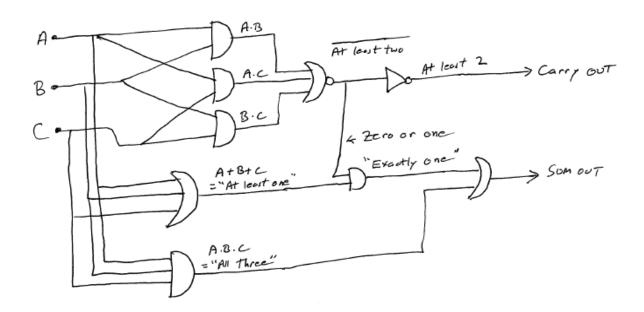

#### **General Scheme for any truth table:**

n inputs (n=3) m outputs (m=2)

need n inverters to make NOT of inputs

need 2<sup>n</sup> n-input AND gates to identify each of the 2<sup>n</sup> rows

need m OR gates to generate the outputs with at most 2<sup>n</sup> inputs, one input for each '1' in the output column.