8:00am Arrival at Point Vicente Rm. / Pick up badges

8:25am Opening remarks: Lars Schreiber

Session 1 (Chair: Susan Coppersmith)

This is an accordion element with a series of buttons that open and close related content panels.

8:30am Keynote presentation: Lieven Vandersypen, “Spin qubit shuttling in perspective"

The quantum information technology has traditionally distinguished flying qubits from standing qubits, which stay in place. With few exceptions, the default picture was that flying qubits are good for quantum communication and standing qubits for quantum computation. Meanwhile, the community has come to appreciate the benefits of being able to move around qubits for computation, as it relaxes the requirements for fault-tolerance and can facilitate more flexible architectures.

Initial ideas for shuttling semiconductor spin qubits around go back 20 years and the first experiments demonstrating the long-distance transfer of single charges were realized 15 years ago. Since then, the field has moved on to demonstrate that both the spin projection and the spin phase can be preserved with high-fidelity. Notably, our group showed spin shuttling over an effective distance of 10 micron in under 200 ns with a fidelity of 99.5%. More recently, we showed that we can operate directly on mobile qubits and explored shuttling as a primitive for the implementation of both single- and two-qubit operations.

This progress is inspiring a new way of thinking about the design of semiconductor spin qubit processors, in which we take full advantage of the freedom offered by shuttling over large and small distances for implementing gates and for achieving enhanced connectivity.

9:15am Zongye Wang, "Non-adiabaticity of electron pick-up process by surface acoustic wave for qubit transport"

Zongye Wang and Xuedong Hu

Surface acoustic waves have been suggested as a carrier to enable remote transport of a single or multiple electrons from one quantum dot to another while maintaining quantum information encoded in the electron’s spin or orbital degrees of freedom. It is widely believed that the process where SAW picks up the electron from a fixed quantum dot is adiabatic, with the electron wavefunction following the instantaneous ground state centered at the collective potential minimum. In this work we explore the adiabaticity of this electron transfer from a static to a moving (or vice versa) dot as we vary system parameters such as relative dot sizes, bias potential, and speed of the moving dot. In particular, we showed that with parameters commonly seen in experiments, the electron pick-up process by SAW is non-adiabatic. The electron dynamics can be described by a highly excited “classical” wave packet. The high degree of excitation could negatively affect the electron spin decoherence, causing loss of quantum information encoded in the spin.

Journal Ref: work in progress

9:40am Ryo Nagai, "Digital-Controlled Conveyor-Belt Spin Shuttling for Scalable Silicon quantum computer”

driven by 10-300 mV amplitudes at ≤100 MHz achieve shuttling fidelities above 99.9%, comparable to the conventional analogue sinusoidal control.

We also estimate the total cryogenic power dissipation and confirmed that the heat dissipation stays below a few milliwatts, well within dilution-refrigerator limits. The proposed method therefore provides a practical path to large-scale, fault-tolerant silicon quantum processors.

This presentation is based on arXiv:2502.20955. This work is supported by JST Moonshot R&D Grant No. JPMJMS2065.

10:05am Coffee break

Please join us for coffee and treats.

Session 2 (Chair: Xuedong Hu)

This is an accordion element with a series of buttons that open and close related content panels.

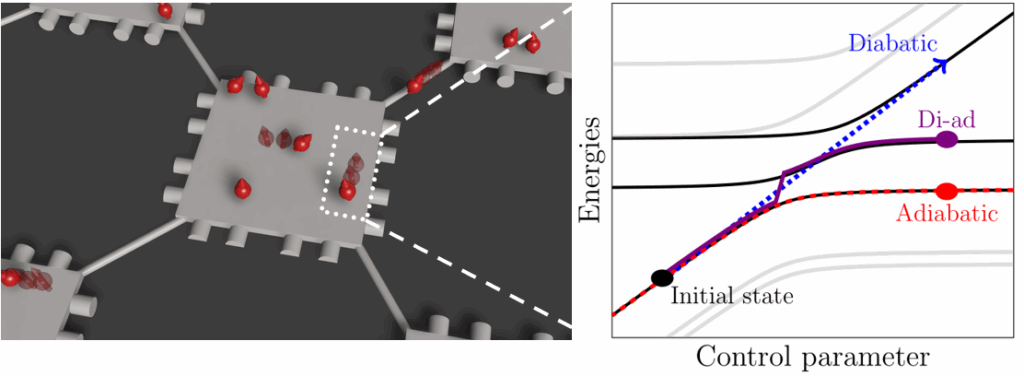

10:25am Maximillian Rimbach-Russ, "Quantum operations of moving spin qubits"

Maximilian Rimbach-Russ

The scalability and power of quantum computing architectures depend critically on the availability and quality of their operations. Mobile qubits are particularly attractive as they enable dynamic and reconfigurable qubit architectures. Such flexibility also relieves architectural constraints, as recently demonstrated in atomic systems based on trapped ions and neutral atoms manipulated with optical tweezers. In solid-state platforms, highly coherent shuttling of electron spins was recently reported [1]. Unwanted transitions into non-computational states such as low-lying orbital or valley states, however, can degrade the fidelity.

The availability of performing high-fidelity quantum operations “on the fly” during the movement instead of stopping reduces waiting times and further increases the potential for scalability. In solid-state platforms, highly coherent diabatic single-qubit operations [2] and two-qubit operations between mobile qubits were recently reported [3]. However, diabatic operations of spin qubits are even stronger limited by unwanted transitions into non-computational states such as low-lying orbital or valley states.

In this talk, I will introduce a new versatile framework for efficient pulse shaping for high-fidelity state transfer in the adiabatic and diabatic limit. The framework allows for high-fidelity state adiabatic transfer in the presence of small anti-crossings [4,5]. Furthermore, we extend the method by interpolating smoothly between adiabatic and diabatic dynamics to minimize unwanted excitations while maximizing desired transitions. We apply the new method to optimize the fidelity of hopping spins in the presence of small tunnel couplings and diabatic single-qubit operations while shuttling.

[1] De Smet, et al. Nat. Nanotechnol. 20, 7, 866.

[2] Wang et al. 385, 6707, 447.

[3] Matsumoto et al. ” arXiv:2503.15434.

[4] Meinersen et al. arXiv:2409.03084.

[5] Meinersen et al. arXiv:2504.08031.

Journal Ref: arXiv:2409.03084, arXiv:2504.08031, and work in progress.

10:50am Mats Volmer, "Reduction of the impact of the local valley splitting on the coherence of conveyor-belt spin shuttling in 28Si/SiGe"

Mats Volmer, Tom Struck, Davide Degli Esposti, Giordano Scappucci, Łukasz Cywiński, Hendrik Bluhm and Lars Reiner Schreiber

Long-range, high-fidelity spin transport remains a key bottleneck for scalable silicon qubit processors [1-3]. Here we demonstrate valley-adaptive conveyor-mode shuttling of a single electron in a purified ²⁸Si/Si₀․₇Ge₀․₃ quantum-well device. By rastering a 40 × 400 nm² area, we map the valley-splitting landscape with nanometer precision [4,5], finding a disorder-limited distribution from 0 to 200 μeV and an autocorrelation length of ≈17 nm, consistent with the dot size. A mere 18 nm lateral path adjustment can bypass low-splitting sites, enabling coherent back-and-forth shuttling over >100 μm; for a 10 μm round-trip at 20MHz we record an infidelity of 6 %. Operating below 20 mT suppresses relaxation hotspots and doubles the dephasing time, confirming recent theoretical predictions [6]. We employ sinusoidal four-phase gate pulses to create a travelling potential wave; single-shot Pauli-spin-blockade readout monitors the singlet probability after each shuttle, yielding real-time valley gaps and coherence decay. Seven parallel traces, each spanning 400 points over 392 nm, provide 2800 valley data points whose histogram follows a Rice distribution, emphasizing random-alloy disorder. Gaussian fits show no spatial correlation beyond 30 nm, guiding future mapping of micron-scale channels. Furthermore, we combine the valley map with a g-factor map to deduce further information. These results validate adaptive route-planning [7] as a practical strategy for integrating micron-scale spin-shuttle interconnects into CMOS-compatible qubit layouts and provide benchmark data for material engineering, velocity optimization and low-field operation.

[1] R. Xue ea., Nat. Commun. 15, 2296 (2024).

[2] T. Struck ea., Nat. Commun. 15, 1325 (2024).

[3] M. de Smet ea., Nat. Nanotechnol. https://doi.org/10.1038/s41565-025-01920-5 (2025).

[4] M. Volmer ea. npj Quantum Inf. 10, 61 (2024).

[5] M. Volmer ea. In preparation (2025).

[6] V. Langrock ea., PRX Quantum 4, 020305 (2023).

[7] M. Losert ea., PRX Quantum 5, 040322 (2024).

11:15am Andrii Sokolov, "Static and Dynamic Simulations of Shuttling for FDX-22 and SiGe quantum devices"

Andrii Sokolov, Conor Power, Xutong Wu, Agostino Aprá, Claude Rohrbacher, Mathieu Moras, Panagiotis Giounanlis, Sergey Amitonov, NodarSamkharadze and Elena Blokhina

As quantum computing architectures advance toward scalability, the ability to coherently shuttle quantum states across large arrays of quantum dotsbecomes essential [1,2]. In particular, spin-based silicon quantum processors require reliable and low-decoherence electron transport methods to enablelong-range interactions and flexible qubit connectivity. This work presents a comprehensive, physics-informed algorithm for optimising bias waveforms usedin conveyor-mode electron shuttling in linear quantum dot arrays. The algorithm integrates self-consistent Poisson–Schrödinger solvers to maintain aconstant ground state energy during transport, thereby preserving coherence and minimising motional excitation. A key innovation is the generation of time-dependent voltage sequences that yield near-constant shuttling velocity, informed by the spatial evolution of quantum states and gate lever-arm parameters.

The method also includes a robust DC bias optimisation scheme to prevent excessive heating and ensure the formation of large, movable quantum dots without decoherence-inducing potential barriers using the QTCAD framework [3]. The approach is validated across multiple device platforms, including FD-SOI, SiMOS and SiGe, revealing how gate geometry, material interfaces, and layout constraints impact transport stability. In FD-SOI systems, the presence of interface-induced potential barriers introduces scattering effects that degrade performance. In contrast, SiMOS and the 6-dot SiGe devices with finely tuned gate geometries exhibit smoother quantum dot motion and more uniform energy landscapes. The study highlights practical limitations of conveyor-mode transport in current technologies and offers concrete guidelines for future device engineering to support scalable, high-fidelity quantum shuttling operations.

In addition, our approach includes investigating valley splitting on shuttling using the QTCAD Atom package.

In this work, we also discuss the 3D Split-operator method [4] to verify the obtained results and to estimate the limiting shuttling speed for the given device geometry.

[1] DOI: 10.1038/s41467-024-49182-4

[2] arXiv: 2406.07267v1

[3] DOI: 10.1063/5.0097202

[4] DOI: 10.1007/978-3-030-50433-5_50

11:40am Lunch

Please join us at the terrace for a buffet lunch and ocean views!

1:00pm Sponsor Presentations

Arque Systems and ML4Q |

Quantum Machines |

Qblox |

Session 3 (Chair: Guido Burkard)

This is an accordion element with a series of buttons that open and close related content panels.

1:20pm Keynote presentation: Simon Benjamin, “Snakes, Loops and Pipelines: Leveraging shuttling for efficient silicon FT QEC"

Although 2D nearest-neighbour architectures can suffice for fault tolerant quantum computing, there are profound benefits to higher connectivity. In silicon spin devices, the ability to physically shuttle the electrons which represent elementary data qubits can enable new ways of realising logical qubits and their interactions. This talk will focus on two paradigms and then discuss generalisations and future directions. I’ll use the surface code (SC) as the example protocol although the methods are not limited to this. The first is the looped pipeline approach where a canonical SC layout (interlaced 2D data and ancilla grids) is employed at the large scale, but at the granular level the data and ancilla elements resolve into complete loops within which streams of electrons perpetually orbit. This increases the density with which logical data is stored — which is of course already a great strength of silicon approaches. A further interesting consequence is that from an application programmer’s point of view there is an effective z-direction even though the physical device is 2D — this can be very helpful in routing information.

The other paradigm is a more radical departure from the canonical SC layout — this “snakes on a plane” approach reformats logical qubits into 1D entities that then move over a 2D lattice. This approach has interesting advantages and challenges, which I will outline. For both paradigms I’ll point out current directions of research, including the idea that both data and/or ancilla qubits can be represented as electron pairs within a parity subspace — as a form of dual rail encoding, this introduces a leakage error that requires correction (effectively, active cooling) but can potentially be helpful for decoders.

“Looped Pipelines Enabling Effective 3D Qubit Lattices in a Strictly 2D Device”, Zhenyu Cai, Adam Siegel and Simon Benjamin, PRX Quantum 4, 020345, 2023

“Snakes on a Plane: mobile, low dimensional logical qubits on a 2D surface”, Adam Siegel, et al, arxiv:2501.02120

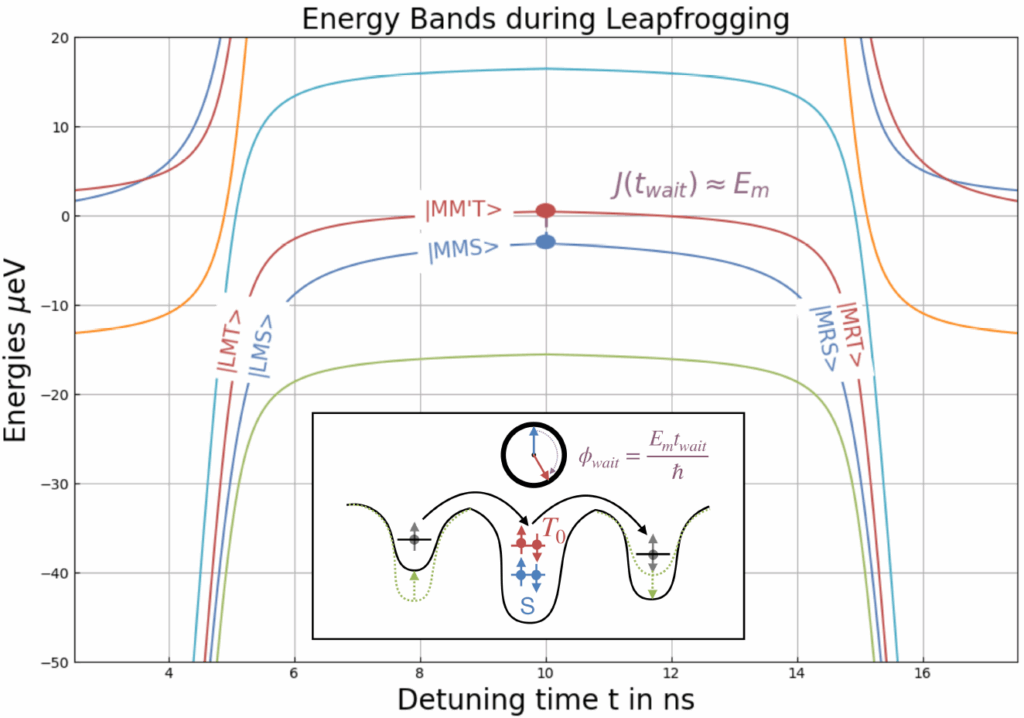

2:05pm Nicklas Meineke, "Spin Qubit Leapfrogging: Shuttling electrons on top of another"

Nicklas Alexander Meineke and Guido Burkard

In recent years spin shuttling has distinguished itself as a promising candidate for achieving high fidelity medium range interactions between spin qubits and presents a powerful tool for enabling scalable semiconductor spin quantum computing architectures in the future. A dominant source of errors encountered during spin shuttling in silicon is the spontaneous of the electron transition into the excited valley state, which leads to unaccounted for dephasing and irregular behaviour during gate application. Modelling the process of a shuttled spin qubit encountering an occupied stationary quantum dot, we investigate the dynamics of the adiabatic (1,1)-(0,2) charge transition in a silicon double quantum dot with non-vanishing inter-valley coupling. This enables us to describe the process of the mobile electron leapfrogging over the stationary one i.e. transitioning from a (1,1,0)- to a (0,1,1)-charge state, occupying a(0,2,0)-state in between. The figure displays this process graphically and also shows the energy bands of the instantaneous eigenstates during the protocol. Here one sees that in the (0,2,0)-configuration the triplets will occupy a valley excited state to circumvent Pauli spin blockade leading to a singlet-triplet splitting approximately equal to the valley splitting in the stationary dot. Consequently this protocol will implement an entangling gate, which can be tuned by waiting in this configuration. For the protocol to be noise-resilient and controllable the middle dot needs to operate at very low valley splitting. As a result this opens up the possibility to isolate and make practical use out of low-valley-splitting hotspots on a wafer, which would otherwise act as sources of error.

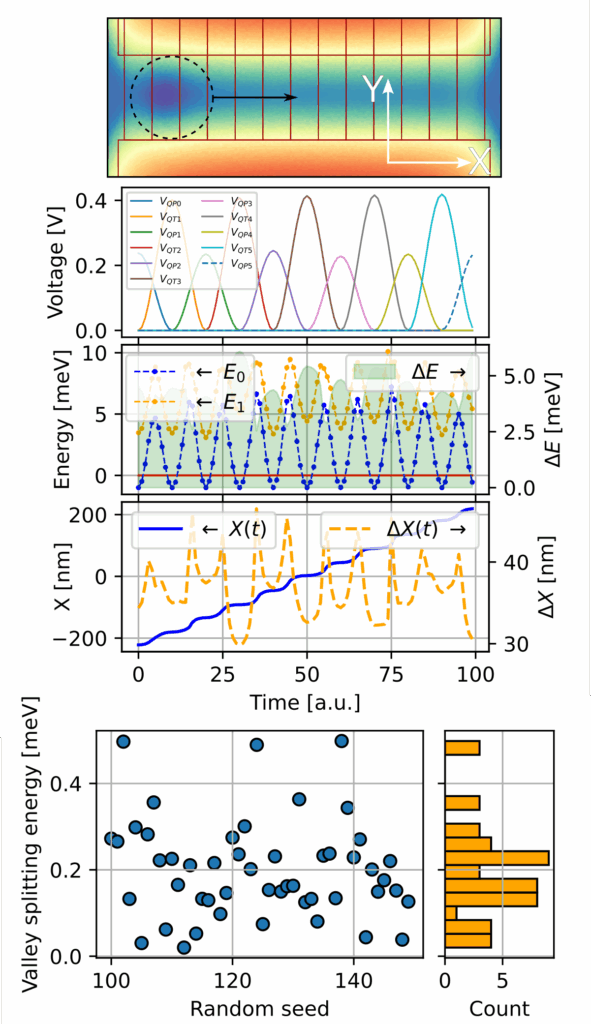

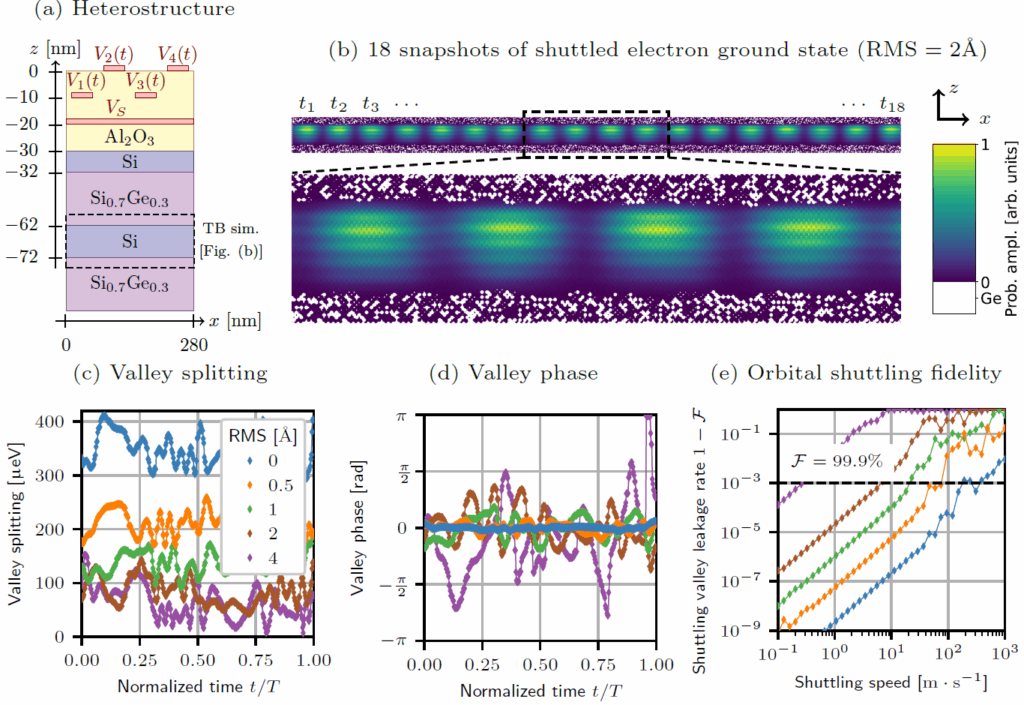

2:30pm Raphaël Prentki, "Multiscale simulations of atomistic-disorder-induced valley-leakage error during electron shuttling"

Raphaël J. Prentki, Pericles Philippopoulos, Mohammad Reza Mostaan and Felix Beaudoin

Electron conveyor-belt shuttling between qubit registers is emerging as a key enabler of scalable silicon spin-qubit quantum computing. As an electron is shuttled over microns or more, it samples angstrom-scale disorder (e.g. random alloying and interface roughness), causing its confinement potential to fluctuate. In turn, the valley splitting and valley phase fluctuate, driving leakage into valley-excited states and capping high-fidelity shuttling speed. Reliable predictions of shuttling fidelities thus require multiscale simulations that link atomistic and mesoscopic physics.

Here, we develop a multiscale simulation workflow based on the QTCAD® package to quantitatively analyze this problem. As a vehicle to this study, we consider the quantum bus (QuBus) architecture; the clavier gate voltages Vi(t) are sinusoidal with period T [Fig. (a)]. First, we obtain the time-dependent confinement potential via finite-element solutions of the Poisson equation. Second, we construct conveyor-belt atomic structures with random alloy disorder and Si/SiGe interface roughness; we relax them within the Keating model to capture strain. Third, we run position-tracked atomistic tight-binding (TB)calculations [Fig. (b)] to extract the electron’s time-dependent valley splitting [Fig. (c)] and valley phase [Fig. (d)]. Finally, these time traces parametrize a time-dependent Schrödinger equation in the valley subspace, wherein the time derivative of the valley phase drives leakage into the valley-excited state, which we solve to obtain the orbital shuttling fidelity [Fig. (e)].

Applying this method, we examine Si/SiGe interfaces with roughness root-mean-square (RMS) values between 0 and 4 Å. We find that the device with pristine interfaces (RMS = 0 Å) achieves orbital fidelities above 99.9% for shuttling speeds below 100 m/s, whereas even modest roughness exponentially degrades fidelity. Our results thus highlight the critical impact of interface roughness on valley phase stability and electron shuttling fidelity.

Journal Ref: work in progress

2:55pm Coffee break

Please join us for coffee and treats.

Session 4 (Chair: Maximillian Rimbach-Russ)

This is an accordion element with a series of buttons that open and close related content panels.

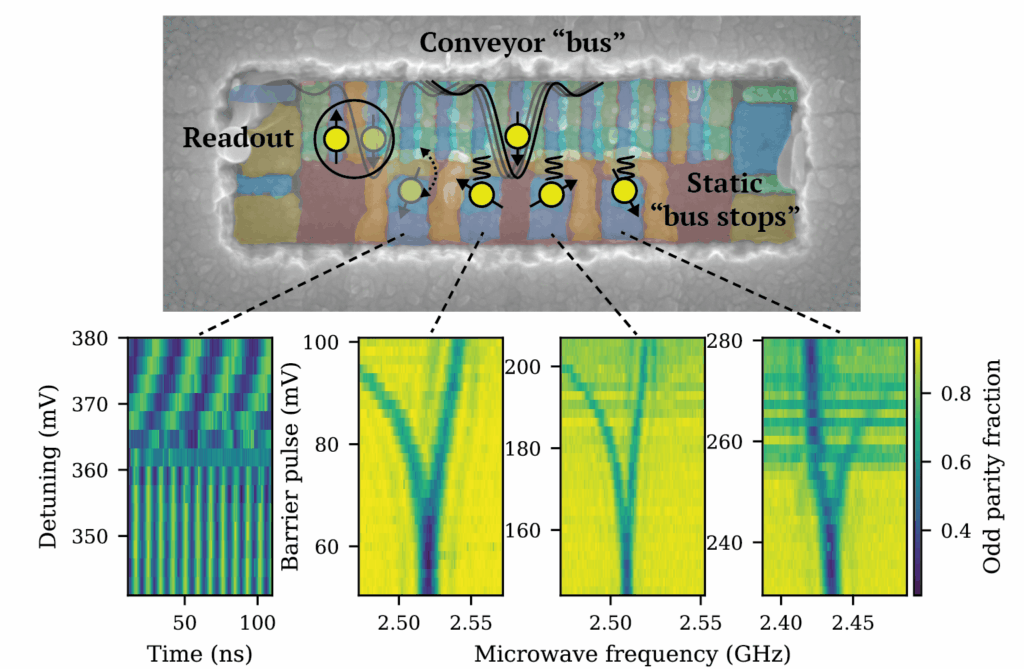

3:15pm Brennan Undseth, "Don't miss the bus: operating a sparse silicon quantum processor"

Brennan Undseth, Nicola Meggiato, Larysa Tryputen, Davide Degli Esposti, Giordano Scappucci and Lieven M. K. Vandersypen

Advances in spin shuttling have established it as a high-fidelity method of coherently transferring spin information at the micron scale, and both bucket-brigade and conveyor-mode spin shuttling have been used as a means of device exploration and characterization. Furthermore, shuttling permits the dynamic reconfiguration of qubit connectivity that is crucial in many large-scale quantum computing architectures. Here, we commission a bilinear array of quantum dots in a 28Si/SiGe heterostructure with two distinct rows of gates: one clavier-style row serving as a conveyor “bus”, and one sparse row of “busstop” quantum dots into which single spins may be parked. The concept of operation is illustrated on top of the device SEM. Using a single readout zone atone end of the conveyor, we explore the conveyor operation and the interdot charge transitions between the conveyor and the bus stops via Ramsey experiments as exemplified in the bottom-left panel. We then use these transitions to virtualize control of the double-dot potentials in a modular fashion. After loading a spin into a bus stop from the conveyor, we can initialize another spin into the conveyor and tune two-qubit logic between the conveyor spin and the bus stop spins. The bottom-middle and right panels illustrate exchange control for three of the bus stops using electric-dipole spin resonance. The conveyor then serves as a proper bus with which to connect beyond-nearest-neighbor spins and acts as a natural ancilla for (up to) four-way quantum non-demolition (QND) parity readout. The experimental techniques developed here showcase the utility of shuttling for tuning sparse arrays far from local charge sensing and spin readout. The universal qubit control, connectivity, and weight-four parity measurements enabled in this architecture provide the necessary ingredients to explore sophisticated protocols such as the [[4,2,2]] error-detecting code.

Journal Ref: work in progress

3:40pm Christian Binder, "Impact of Device Imperfections on Charge Transport and Valley Excitations During Electron Shuttling in Si/SiO2"

Christian Walter Binder, Jack James Turner, Guido Burkard and Andrew Fisher

There have been extensive theoretical studies and high-fidelity experimental demonstrations of shuttling in Si/SiGe, but considerably less work has been done on this topic in Si/SiO. To address this, we build on previous 2D simulation work by performing full 3D modelling of conveyor-mode charge shuttling in realistic Si/SiO2 devices with charged defects, gate imperfections, and roughness at the oxide interface. Using solutions to the Poisson and time-dependent Schrödinger equations for different shuttling speeds and gate voltages, we find that positive defects directly in the shuttling path capture passing electrons when using lower clavier gate voltages of 250mV. Increasing the conveyor confinement with gate voltages of 500mV ensures the passing electrons escape the trap, but they emerge in an orbitally excited state potentially opening spin-flip pathways via spin-orbit coupling and phonon relaxation. On the other hand, single negative defects don’t disrupt transport by knocking electrons into adjacent minima, but do induce orbital excitation for lower clavier gate voltages of 250mV. These excitations are suppressed by increasing the confinement, and so are not expected to present an obstacle to charge shuttling. Our simulations also show charge shuttling remains robust against 30% variations in clavier gate footprint and interface roughness as high as rms=0.9nm. However, when we use these modelling tools to compute the valley splitting and phase for different interfaces, we find that even modest roughness creates adversarial valley landscapes with low splitting and rapidly changing phase. We observe that the electron is highly susceptible to valley excitations when shuttling across these interfaces for even slow shuttling speeds, which may lead to spin-dephasing and leakage out of the computational subspace. This highlights the importance of mitigation strategies currently being explored in the Si/SiGe literature to Si/SiO2 devices, for example using variable shuttling speeds and paths or compensating for channel-specific dephasing with Z-rotations.

Journal Ref: work in progress

4:05pm Stefano Bosco, "Spin-orbit-enabled universal two-qubit gate set on moving spins"

David Fernández-Fernández, Yuta Matsumoto, Lieven Vandersypen, Gloria Platero and Stefano Bosco

Shuttling spin qubits in systems with large spin-orbit interaction (SOI) can cause decoherence and errors during motion. However, in this work, we demonstrate that SOI can be harnessed to implement a universal set of high-fidelity two-qubit (2Q) gates. We consider two spin qubits defined in a semiconductor double quantum dot that are smoothly, electrically moved toward each other. By controlling the shuttling speed and waiting times, and leveraging strong intrinsic or extrinsic SOI, we show that a universal set of high-fidelity 2Q gates can be realized. Crucially, performing 2Q operations during qubit transport enables direct and flexible distributed entanglement generation between distant sites, alleviating the need for complex static coupling schemes and lengthy gate sequences. Our findings establish a practical route toward direct, universal 2Q gate implementation via spin shuttling, significantly reducing control overhead in scalable quantum computing architectures.

Journal Ref: work in progress